# CSc 553 Principles of Compilation 23: Register Allocation Department of Computer Science University of Arizona Copyright © 2011 Christian College

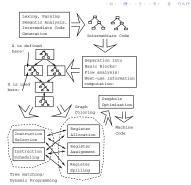

## Introduction

Register Allocation by Graph Coloring

- Register allocation is difficult:

- Machines have weird instruction sets, register pairs (two consecutive registers that are the source or destination in an instruction), register classes (address, integer, index, floating)....

- Optimal solutions to the register allocation problem is NP-complete.

- Most compilers use complicated ad hoc heuristic register allocation algorithms. It would be helpful if we had a good model for register allocation the way we have finite automata for lexical analysis, attribute grammars for semantic analysis, etc.

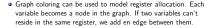

- · We can model register allocation using undirected graphs.

- Model register allocation as a graph coloring problem. Each color represents an available register.

- Create a graph node for each variable. If variables a and b are active (live) at the same point, they cannot be assigned to the same register. Add an edge (a, b) to the graph.

- Look for a k-coloring (k =# registers) of the graph. Assign colors so that neighboring nodes have different colors.

- If we cannot k-color our graph, we:

- Select a node (variable) n whose value we're willing to spill,

- Insert spill code,

- Delete node n and its edges,

- Look for a k-coloring.

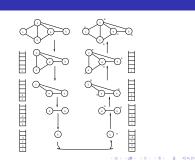

#### The Interference Graph I

- The interference graph (an undirected graph where the nodes are the variables of the program) models which variables cannot be allocated to the same register.

- Connect a and b if a is live at a point where b is defined.

| (1) | a | := | 5 |   |   |

|-----|---|----|---|---|---|

| (2) | d | := | 9 | + | a |

| (3) | е | := | a | + | d |

| (4) | Ъ | := | d | + | a |

| (5) | f | := | е | + | 6 |

| (6) | С | := | Ъ | + | f |

|     |   |    |   |   |   |

## The Interference Graph II

- Register allocation is a bit like room scheduling.

- Room scheduling:

- We have a set of rooms (registers).

- We have a set of classes (variables) to fit into the rooms.

- Two classes that meet at the same time cannot be allocated to the same room

- The difference is that in room scheduling there can be no spilling; no-one gets to have their lecture in the park!

- A variable's live range

- starts at the point in the code where the variable receives a value, and

- ends where that value is used for the last time.

48 × 42 × 42 × 2 × 99.0

# Chaitin's Coloring Algorithm

1011612131313190

## Coloring Example I (a) -k=3

## Coloring Example I (b) -k=2

#### Coloring Example II -k=2

# Precoloring

#### Precolored Nodes I

- Sometimes we will want to express that a particular variable must reside in a particular register. For example, if variable a is being passed as argument 1 to procedure P on the SPARC, we'd want to express that a must reside in register %00, and nowhere else.

- Similarly, sometimes we want to express that a particular variable must not reside in a particular register. For example, a floating point variable should not be in an integer register.

- Such variables are precolored.

- We augment the interference graph with nodes for each available register, and an edge between variable a and register r if a cannot be allocated to r.

#### Precolored Nodes II

VAR x, y : INTEGER; VAR a, b : REAL; x := 100; a := 1.0; b := a + 5.2; y := x + 50; P(y,a);

- We have two integer registers  $r_1$  and  $r_2$ , and two FP registers  $f_1$  and  $f_2$ .

- Procedure actuals are passed in registers: y in r<sub>1</sub> and a in f<sub>1</sub>.

#### Precolored Nodes III

```

VAR x, y : INTEGER;

VAR a, b : REAL;

x := 100;

a := 1.0;

b := a + 5.2;

y := x + 50;

P(y,a);

```

- We color y and r<sub>1</sub> red (R), x and r<sub>2</sub> green (G).

- We color a and f<sub>1</sub> blue (B), b and f<sub>2</sub> yellow (Y).

#### Register Coalescing

- Register coalescing is a kind of copy propagation that removes register copies.

- Search the intermediate code for copies S<sub>j</sub> ← S<sub>i</sub> such that S<sub>j</sub> and S<sub>i</sub> don't interfere with each other.

- Modify any instruction  $S_i \leftarrow \cdots$  to  $S_j \leftarrow \cdots$  and merge the interference graph nodes for  $S_i$  and  $S_i$ .

# Register Coalescing

# Splitting Live Ranges

#### Splitting Live Ranges

- . If we use the same variable for several unique tasks (e.g. i for all for-loops) the interference graph is overly constrained.

- Instead we let each graph node represent a unique use of a variable.

```

x := 100:

a := x * 2;

PRINT a:

x := 200:

b := x + 5:

PRINT b:

x_1 := 100;

a := x_1 * 2;

PRINT a;

x_2 := 200;

b := x_2 + 5;

PRINT b:

```

# Building the Interference Graph

#### Building the Interference Graph I

- We start by performing a liveness analysis.

- in [B] Variables live on entrance to B.

- out [B] Variables live on exit from B.

- . def [B] Variables assigned values in B before the variable is used.

- use [B] Variables whose values are used before being assigned to.

Data-flow Equations:

$$\begin{array}{lll} \text{in}[B] &=& \text{use}[B] \cup (\text{out}[B] - \text{def}[B]) \\ \text{out}[B] &=& \bigcup_{\text{succs S of } B} \text{in}[S] \end{array}$$

#### Building the Interference Graph II

. Then we build the graph. For efficiency, we store it both as an adjacency matrix, and as adjacency lists.

```

FOR all basic blocks b in the program DO

live := out[b]:

FOR all instructions I \in b, in reverse order DO

FOR all d \in def(I) DO

FOR all l \in \text{live} \cup \text{def}(l) DO

add the interference graph edge \langle I, d \rangle;

live := use(I) \cup (live - def(I));

```

40 × 40 × 42 × 42 × 2 × 900

920 S (5) (5) (6)

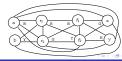

#### Building the Interference Graph V

Here's the finished interference graph:

# Summary

- · Read the Tiger Book, Chapter 11, Register Allocation.

- The Dragon book: 513-521, 528-546, 554-559.

- Preston Briggs' thesis: Register Allocation via Coloring, http://cs-tr.cs.rice.edu:80 /Dienst/Repository/2.0/Body/ ncstrl.rice\_cs/TR92-183/postscript.

- Steven Muchnick, Advanced Compiler Design and Implementation. Chapter 16, pp. 481–525.

- The coloring algorithm assigns colors so that no neighboring nodes receive the same color.

- Optimal coloring is NP-complete (at least for global register allocation), so we need a heuristic algorithm that produces a good approximation.

Homework

Register Allocation by Graph Coloring

#### Homework III - Graph Coloring

# Homework IV - Graph Coloring

Construct the interference graph for the basic block below. and show the coloring produced by Chaitin's algorithm when two and three registers are available. Spill costs are X=3,Y=1,Z=2,V=2.

```

X := 5:

Y := X + 3:

Z := X + 5:

V := Y + 6:

X := X + Y:

X := V + Z:

```

procedure body below, and show the global coloring produced by Chaitin's algorithm when two and three registers are available. Spill costs are X=1,Y=2,Z=3,W=1,V=2. X := · · · · · 7. := · · · · :

· Construct the flow-graph and the interference graph for the

## BEGIN

```

IF e_1 THEN Z := \cdots;

ELSE Y := · · · :

ENDIF:

· · · := X: · · · := Y:

W := \cdots : V := \cdots :

IF e> THEN ... := W: ... := Z:

ELSE · · · := V:

ENDIF:

```

FND

#### Exam Problem I(a) (415.430 '95)

## Exam Problem I(b) (415.430 '95)

· · · := V + W:

X := 5:

Consider the following basic block:

```

X := 5:

A := X + 5:

B := X + 3:

V := A + B:

A := X + 5:

Z := V + A:

PRINT Z. V. A:

```

Construct the register interference graph for the block.

4 How many colors are necessary to color the graph optimally without register spills? 4 m 2 m 4 m 2 m 4 m 2 m 9 q 0

A := X + 5:B := X + 3: V := A + B: A := X + 5:Z := V + A: PRINT Z. V. A:

Show the graph after it has been colored with Chaitin's algorithm using 2 colors (Red and Blue). The spill-costs are: A=1, Z=2, B=3, V=2, X=4.

(B)

10 10 10 12 12 12 12 1990

## Exam Problem II/a (415.730 '96)

#### Exam Problem II/b (415.730 '96)

#### Consider the following basic block:

```

A := 5;

F := A + 1;

E := F + 5;

B := F * A;

PRINT B + E + A;

D := E + 5;

PRINT E;

C := D + B;

```

PRINT E + C:

Construct the register interference graph for the block.

4 How many colors are necessary to color the graph optimally without register spills?

Show such an optimal coloring!

Show the graph after it has been colored with Chaitin's algorithm using 2 colors (Red and Blue). The spill-costs are: C=1, D=2, E=3, B=A=4, F=5.

(A)