#### CSc 553

Principles of Compilation

X11: 11 Cocktail and BEG

Department of Computer Science University of Arizona

Copyright © 2011 Christian Collberg

# Code Generation with BEG

#### BEG and Cocktail I

- We'll talk about a code generator generating system called BEG

- BEG is part of a larger compiler construction toolset called Cocktail. Cocktail has tools that construct parsers, scanners, semantic analysers, intermediate code generators and machine code generators.

- Most of the Cocktail tools are now commercial products, but there are still some free early versions around on the net.

- BEG is a program which takes as input a specification consisting of code generation rules, a description of the target architecture, and a description of the intermediate representation.

#### BEG and Cocktail II

- Based on the machine description BEG produces a code generator which operates by pattern-matching on the intermediate representation.

- One can choose between several (at least two...) types of register allocators.

- The code generator constructed by BEG takes as its input a sequence of expression trees. Output can be just about anything; we will produce textual assembly code.

- The code generator takes care of (almost) all aspects of code generation: instruction selection, register allocation, register assignment, and register spilling.

- The next slide shows the overall structure of a compiler built by Cocktail.

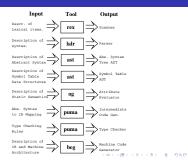

#### Cocktail Generated Files

#### Cocktail Tools

(B) (B) (B) (B) (B) (B) (O)

#### The Phases of Beg I

- The code generator generated by BEG runs in three phases.

- The first phase uses pattern matching to construct a minimal cover of the input tree: the code generator will find the set of code generator rules which will produce the cheapest (fastest) code sequences. BEG does this by covering the input tree with the cheapest sequence of patterns.

- . The second phase allocates register.

- The third phase generates the actual code.

- Another way of thinking about a minimal cover is to say that the selected patterns reduce the input tree to the empty tree by deleting matched parts of the input tree.

40 × 40 × 42 × 42 × 2 × 990

#### Intermediate Code

- When we build the code generator with BEG, BEG generates a module Sparc.md/mi which is the interface to the code generator.

- At compile-time we call procedures in this module to build the intermediate code tree.

- The code generator generated by BEG assumes that the intermediate code is in a tree format. The structure of the tree-nodes is described by a specification.

- The + (\*)-sign makes the operator (non-)commutative (Plus is commutative since a + b ≡ b + a).

- Parentheses indicate input attributes, data passed from the front end to the code generator.

There are several alternative ways of thinking about the actions taken by BEG during code generation:

- Find a set of patterns that covers the input tree, such that the total cost is minimized.

- Build a tree (identical to the input tree) out of the available patterns, such that the total cost of the new tree is minimized.

- Apply the patterns to the input tree, replacing the matched part of the tree with the right hand side of the pattern, until the tree is consumed. Chose the set of patterns with minimal cost.

These simple rules all contain three parts: a pattern, a cost, and an emit-part. The pattern-part describes a sub-tree which the rule matches, the emit-part describes the instructions to be generated by the rule, and the cost-part describes the cost of executing these instructions.

#### Explanations:

Rule 1, for example, states that on the SPARC there is an add-instruction which adds two registers into a third, and which executes in one (1) machine cycle.

D 1 (#1) (2) (2) (2)

- Rule 2 says that we can load the value at a given address into a register using the 1d-instruction. Address is a SPARC addressing mode which has several different forms.

- Rule 5 shows how we can load an integer value into a register using the set pseudo-operation.

- Rule 6 is known as a chain-rule. It generates no code but simply states how we may transform a value from one form to another. In this case the rule states how we can transform a register into the addressing mode Address. The Modula-2-code in the EVAL-part is executed during the code generator's cover phase, whereas the code in the EMIT-part is executed during the output phase.

#### Beg Tree Patterns II

- A Beg pattern is normally a sub-tree where the leaves are non-terminals.

- A non-terminal represents a storage class on the machine, i.e. a register or some other addressing mode.

- Most patterns have a result non-terminal, which describes the type of storage class in which the instruction returns its result.

- Top-level patterns are distinguished by the fact that they do not have a result non-terminal. They therefore only match the root of an input expression tree.

## BEG Example I (d)

- A chain rule transforms a value from one storage class to another. Often this can be done without generating any code. For example, if one instruction returns its result in a register, and the next instruction requires its argument in an address (e.g. a Sparc addressing mode which is either a register, the sum of two registers, or the sum of a register and a small offset), then we can use a chain rule that maps a register non-terminal to an address (without producing any code) rather than introducing an explicit rule for each instruction of that kind.

- We can use the same technique to handle machines with more than one register class (Address and Data Registers for the MC68XXX architecture, for example).

set A, %10

ld [%10], %10

set 314, %11

add %10, %11, %10

set A, %11

st %10, [%11]

#### **Building Beg Specifications**

A working BEG specification can be extended with new rules that produce better code in special cases.

Structure of BEG Specifications

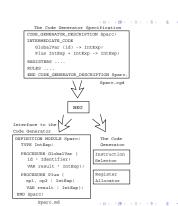

## Structure of Sparc.cgd

The main BEG specification for the SPARC architecture is stored in a file Sparc.cgd. It has the following global structure:

CODE\_GENERATOR\_DESCRIPTION Sparc; INTERMEDIATE\_REPRESENTATION NONTERMINALS IntExp; OPERATORS

Intermediate code format

REGISTERS

Description of registers AVAIL (Available registers); NONTERMINALS

Description of addressing modes

Code generation rules INSERTS

Code to be inserted in generated modules END CODE\_GENERATOR\_DESCRIPTION

# Intermediate Format

# This is how the tree-nodes are described.

CODE\_GENERATOR\_DESCRIPTION Sparc; INTERMEDIATE\_REPRESENTATION:

NONTERMINALS IntExp;

#### OPERATORS

Integer (value: INTEGER)-> IntExp: GlobalVar (id: Identifier) IntExp: Load IntExp IntExp: Store IntExp \* IntExp: IntExp + IntExp -> IntExp: P1118

END CODE\_GENERATOR\_DESCRIPTION ···.

# Registers and Addr. Modes

CODE\_GENERATOR\_DESCRIPTION Sparc;

REGISTERS

IO.I1.I2.I3.I4.I5.I6.I7. .... i5.i6.i7: AVAIL (10..17.i0..i5.i7.o0..o5.g1..g6): NONTERMINALS

Register REGISTERS (I0.I1.I2....i5....): Greg REGISTERS (g1,g2,g3,g4,...); Address **ADRMODE**

COND\_ATTRIBUTES (val : INTEGER) (reg1 : Register; reg2 : Register);

RegOrlmm ADRMODE COND ATTRIBUTES (val : INTEGER)

(reg : Register): IntConst13 COND\_ATTRIBUTES · We need to know the addressing modes the machine has and which registers are available.

Sparc Architecture

Integer Register global (%g0, %g1,..., %g7)

> local (%10, %11,..., %17) input (%i0, %i1,..., %i7) output (%o0, %o1,..., %o7)

Floating Point Register (%f0, %f1,..., %f31)

Address reg, + reg, reg<sub>1</sub> + const<sub>13</sub>

const<sub>13</sub>

Register or Immediate reg<sub>1</sub>

const<sub>13</sub>

# **BEG Rules**

RIIIF

COST

CONDITION

RULE Pattern consisting of register classes, addressing modes. operators, etc.

CONDITION Condition evaluated during cover phase. If result is FALSE rule will not be used.

COST Cost (in number of cycles) of using rule. CHANGE Registers affected by generated code.

EVAL Code to evaluate attributes, build addressing modes, etc.

EMIT Code to generate target code.

arg,

arg<sub>2</sub> result

{ Boolean Modula-2-expression }: Integer,

CHANGE ( Affected registers ): Cover phase Modula-2-code \; FVΔI **EMIT** Output phase Modula-2-code \: 920 S (S) (S) (B) (B)

# Advanced BEG Rules I

EMIT {Write("mul...");}

EMIT {Write("...");}

Advanced BEG Rules III

COST 4;

COST 4:

COST 0:

# Advanced BEG Rules II

argument is in one of the specified registers.

(fold) constant expressions.

RULE Plus Integer.a Integer.b -> Integer.c

EVAL {c.value := a.value + b.value}

The mul instruction requires its arguments to be in registers %o0 and %o1, and returns its result in register %o0. Admissible Registers II:

RULE Instr Reg.a(o0..06) -> Reg.b(o0)

Constant Folding:

Rule 9:

The Modula-2 code in in the EVAL part of a rule is executed

during the cover phase. It can therefore be used to evaluate

For example, an expression a + 2 \* 3 would be translated into code for a + 6, with 2 \* 3 evaluated at compile time.

Admissible Registers I:

. In order to use this rule, Beg has to make sure that the

RULE Mult Reg.a(o0) Reg.b(o1)->Reg.c(o0)

# Advanced BEG Rules IV

EMIT {Write("...");}

RULE Call.c Arg;

CHANGE (g1..g6); EMIT {Write("call...");}

COST 2;

COST 4:

A BEG rule can be given an arbitrarily complex pattern. The pattern part of a rule is actually a preorder traversal of a tree pattern. . The following example shows how we can specify a multiply-and-add instruction:

\_\_\_\_\_ Complex Patterns: \_\_\_\_\_

Registers Affected by Side-Effects:

Computed Registers:

The expression returns a suitable register. This is useful when

101 (#1 (2) (2) (3) 3 000

A procedure call affects all global registers.

RULE Instr Reg.a -> Reg.c({Mod-2 Expr})

passing parameters in registers.

RULE Plus Reg.a Mult Reg.b Reg.c -> Reg.d COST 2:

EMIT {write("MADD ...");}

40 × 40 × 42 × 42 × 2 × 900

- The last part of a BEG specification consists of instructions that inserts extra code into the generated modules.

- Often this code consists of IMPORT statements that makes it possible for the generated modules to find types and procedures defined by us.

- For every module M generated by BEG, you can insert code into its definition and implementation modules. This is done in so called insertion points (Ip):

There are special insertion points called IpInOut (for inserting IO routines) and IpNoReg (for inserting code to call when register allocation fails).

Example: IBM370

```

CODE_GENERATOR_DESCRIPTION Sparc;

INSERTS

IpInOut {

FROM AsmFile IMPORT

Create,...,FatalError;

}

IpIR_4 {

FROM GcgBase IMPORT

Identifier, Condition;

}

IpIR_1 {

FROM GcgBase IMPORT Identifier,...,

PrintCondition;

}

IpNoReg {

FatalError ("Reg alloc failed.");

HALT;

}

```

#### Example - IBM370 I

```

CODE_GENERATOR_DESCRIPTION IBM370;

INTERMEDIATE_REPRESENTATION

NONTERMINALS Value;

OPERATORS

Constant ( v : INTEGER )

-> Value:

Plus

Value + Value -> Value:

Value + Value -> Value;

Mullt.

AddressPlus

Value * Value -> Value;

BlockBase

-> Value:

Content

Value

-> Value:

Assign

Value * Value;

```

```

REGISTERS

RO,R1,R2,R3,R4,R5,R6,R7,R8,R9,R10,R11,

R12,R13,R14,R15,

D0(R0,R1),D2(R2,R3),D4(R4,R5),D6(R6,R7),

D8(R8,R9),D10(R10,R11),D12(R12,R13),

D14(R14,R15),F0,F1,F2,F3,F4,F5,F6,F7,

DF0(F0,F1),DF2(F2,F3),DF4(F4,F5),DF6(F6,F7);

NONTERMINALS

Register REGISTERS (R0,R1,R2,R3,R4,R5,R6,R7,R8,R9,R10,R11,R12);

Double REGISTERS (D0,D2,D4,D6,D8,D10);

RegSum ADRMODE (r:Register; s:Register);

```

O 2 (#2 (2) (2) 2 (9)

40 × 40 × 42 × 42 × 2 × 900

## Example – IBM370 IV

# Summary

## Readings and References

#### Summary

- Read the Tiger Book, Chapter 9, Instruction Selection.

- Read "Emmelmann, Schröer, Landwehr: BEG A generator for Efficient Back Ends", PLDI '89.

- Or, read the Dragon Book, pp. 572-580.

• In the Sparc example, the val-attributes in the Address, RegOrImm, and IntConst13 addressing modes are specified as condition attributes. This means that this attribute gets its value during the code generator's cover phase. The register attributes, on the other hand, get their values during the output phase.