### CSc 553 — Principles of Compilation

20: Code Generation III

Christian Collberg

Department of Computer Science

University of Arizona

collberg@gmail.com

Copyright © 2011 Christian Collberg

February 24, 2011

1

## Trivial Code Generation

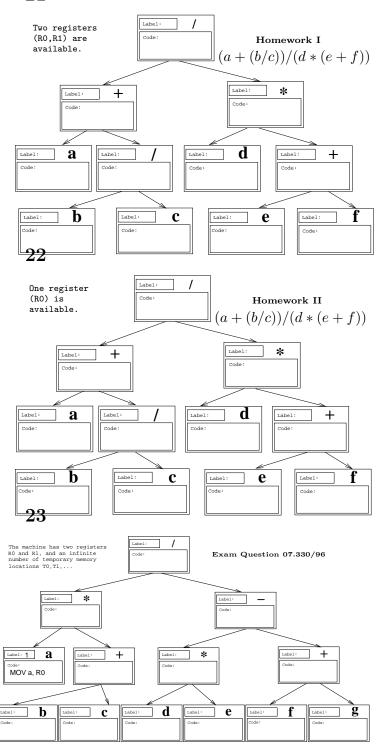

#### 2 Generating Code From Trees

- ullet To generate code from expression trees, traverse the tree and emit machine code instructions.

- For leaves (which represent operands), generate load instructions. For interior nodes, generate arithmetic instructions.

- Assume an infinite number of registers  $\Rightarrow$  easy algorithm!

- ullet Each tree node N has an attribute 'R', the register into which the subtree rooted at N will be computed.

3

## Generating Code From Labeled Trees

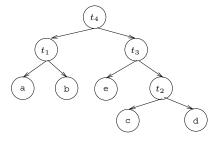

#### 4 Optimal Ordering For Trees I

- We can generate 'optimal' code from a tree. 'Optimal' in the sense of 'smallest number of instructions generated'.

- The idea is to reorder the computations to minimize the need for register spilling.

| First Order                            | Second Order                                                      |  |  |

|----------------------------------------|-------------------------------------------------------------------|--|--|

| $t_1 := a + b$                         | $t_2 := c + d$ $t_3 := e - t_2$ $t_1 := a + b$ $t_4 := t_1 - t_3$ |  |  |

| $t_2 := c + d$                         | $t_3 := e - t_2$                                                  |  |  |

| $t_3$ := $e$ - $t_2$                   | $t_1 := a + b$                                                    |  |  |

| $t_3 := e - t_2$<br>$t_4 := t_1 - t_3$ | $t_4 := t_1 - t_3$                                                |  |  |

| !                                      | 1                                                                 |  |  |

#### 5 Optimal Ordering For Trees II

• Assume two registers available. The first ordering evaluates the left subtree first, and has to spill R0 to have enough registers available for the right subtree.

| First Order            | Second Order           | First Order |                     | Second Order |           |

|------------------------|------------------------|-------------|---------------------|--------------|-----------|

| t <sub>1</sub> :=a+b   | $t_2$ :=c+d            | MOV         | a, R0               | MOV          | c, RO     |

| $t_2$ :=c+d            | $t_3$ :=e- $t_2$       | ADD         | b, R0               | ADD          | d, RO     |

| $t_3$ :=e- $t_2$       | $t_1$ :=a+b            | MOV         | c, R1               | MOV          | e, R1     |

| $t_4$ := $t_1$ - $t_3$ | $t_4$ := $t_1$ - $t_3$ | ADD         | d, R1               | SUB          | RO, R1    |

|                        |                        | MOV         | RO, $t_1$           | MOV          | a, RO     |

|                        |                        | MOV         | e, RO               | ADD          | b, RO     |

|                        |                        | SUB         | R1, R0              | SUB          | RO, R1    |

|                        |                        | MOV         | $\mathtt{t}_1$ , R1 | MOV          | RO, $t_4$ |

|                        |                        | SUB         | RO, R1              |              |           |

|                        |                        | MOV         | R1, $t_4$           |              |           |

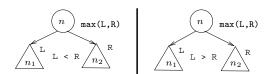

#### 6 The Tree Labeling Phase I

• The algorithm has two parts. First we label each sub-tree with the minimum number of registers needed to evaluate the subtree without any register spilling.

$\_$  The Labeling Algorithm:  $\_$

- n is a left leaf  $\Rightarrow$  label(n) := 1;

- n is a right leaf  $\Rightarrow$  label(n) := 0;

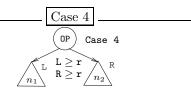

- n's children have labels  $l_L \& l_R$ :

- $-l_L \neq l_R \Rightarrow label(n) := max(l_L, l_R)$

- $-l_L = l_R \Rightarrow label(n) := l_L + 1$

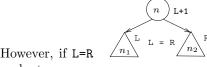

#### The Tree Labeling Phase II

- If we have a node n with subtrees  $n_1$  and  $n_2$  with L=label( $n_1$ ) & R=label( $n_2$ ) & L<R then we can first evaluate  $n_2$  into a register Reg using R registers. Then we use R-1 registers to evaluate  $n_1$ .

- Similarly, if L>R then we can first evaluate  $n_1$  into a register Reg and use the remaining R-1 registers for  $n_2$ .

We'll need one extra register to hold the result of  $n_1$  while we

#### The Generation Phase I

• gencode(n) generates machine code for a subtree n of a labeled tree T.

MOV M, R Load variable M into register R.

MOV R, M Store register R into variable M.

OP M, RCompute R := R OP M.  $OP \in ADD$ , SUB, MUL, DIV.

OP R2, R1 Compute R1 := R1 OP R2.

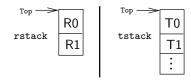

- A stack rstack initially contains all available registers. gencode(n) generates code for subtree n using the registers on rstack, computing its value into the register on the top of the stack.

- A stack tstack of temporary memory locations is used for register spilling.

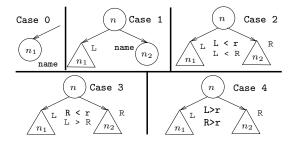

#### The Generation Phase II 9

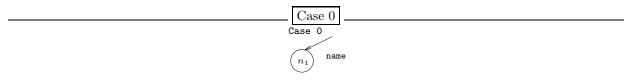

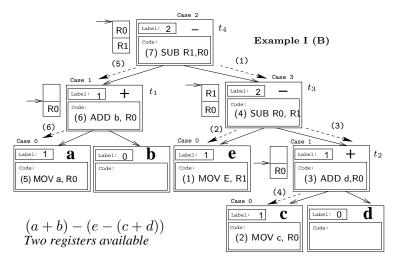

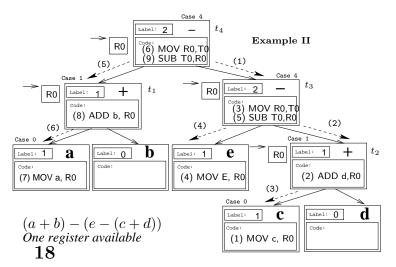

Case 0 A leaf n is the leftmost child of its parent.

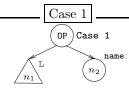

Case 1 A leaf  $n_2$  is the rightmost child of its parent.

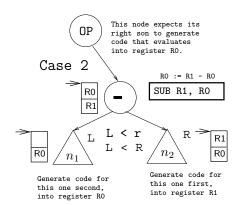

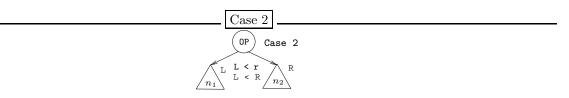

Case 2 A right subtree  $n_2$  requires more registers than the left subtree  $n_1$ .

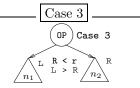

Case 3 A left subtree  $n_1$  requires more registers than the right subtree  $n_2$ .

Case 4 Both subtrees require registers to be spilt.

#### 10 The Generation Phase III

1. Generate a load instruction to load the variable into a register: MOV name, top(rstack)

- 1. Generate code for  $n_1$  into register top(rstack), i.e. call gencode( $n_1$ ).

- 2. Generate OP name, top(rstack)

#### 11 The Generation Phase IV

- $n_1$  can be evaluated without spilling, but  $n_2$  requires more registers than  $n_1$ .

- We swap the two top registers on rstack, evaluate  $n_2$  into top(rstack), remove the top register, then evaluate  $n_1$  into top(rstack). Restore the stack.

- 1. swap(rstack),  $gencode(n_2)$

- 2. R := pop(rstack)

- 3. gencode  $(n_1)$

- 4. Generate OP R, top(rstack)

- 5. push(rstack, R), swap(rstack)

#### 12 The Generation Phase V

- $n_2$  can be evaluated without spilling, but  $n_1$  requires more registers than  $n_1$ .

- We evaluate  $n_1$  into top(rstack), remove the top register, then evaluate  $n_2$  into top(rstack).

- 1. gencode  $(n_1)$

- 2. R := pop(rstack)

- 3. gencode( $n_1$ )

- 4. Generate OP top(rstack), R

- 5. push(rstack, R)

#### 13 The Generation Phase VI

- Neither  $n_1$  nor  $n_2$  can be evaluated without spilling,

- We evaluate  $n_2$  into a temporary memory location top(tstack), and then we evaluate  $n_1$  into top(rstack).

- 1. gencode  $(n_2)$

- 2. T := pop(tstack)

- 3. Generate MOV top(rstack), T

- 4. gencode  $(n_1)$

- 5. push(tstack, T)

- 6. Generate OP T, top(rstack)

**14**

## Examples

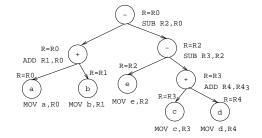

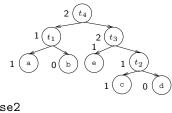

### 15 Example I (A)

```

gencode(t_4)

[R1,R0]

case2

gencode(t_3)

[RO,R1]

case3

gencode(e)

[RO,R1]

case0

MOV e, R1

gencode(t_2)

[RO]

case1

gencode(c)

[RO]

case0

MOV c, RO

SUB RO, R1

gencode(t_1)

[RO]

case1

gencode(a)

[RO]

case0

MOV a, RO

RO

ADD b,

SUB R1, R0

```

#### 16

17

# Summary

### 19 Readings and References

• This lecture is taken from the Dragon Book:

$\textbf{Local Optimization: } 530\text{--}532,\,600\text{--}602.$

### 20 Summary I

• Why do we swap registers in Case 2?