## OPERATING SYSTEM SUPPORT FOR HIGH-SPEED NETWORKING

(Ph.D. Dissertation)

Peter Druschel

94 - 24

August 1994

Department of Computer Science The University of Arizona Tucson, Arizona 85721

This research was supported by National Science Foundation Grant CCR-9102040, DARPA Contract DABT63-91-C-0030, and Sun Microsystems Inc.

# OPERATING SYSTEM SUPPORT FOR HIGH-SPEED NETWORKING

by

Peter Druschel

Copyright© Peter Druschel 1994

A Dissertation Submitted to the Faculty of the DEPARTMENT OF COMPUTER SCIENCE In Partial Fulfillment of the Requirements For the Degree of DOCTOR OF PHILOSOPHY In the Graduate College THE UNIVERSITY OF ARIZONA

$1 \ 9 \ 9 \ 4$

#### OPERATING SYSTEM SUPPORT FOR HIGH-SPEED NETWORKING

Peter Druschel, Ph.D. The University of Arizona, 1994

Director: Larry L. Peterson

The advent of high-speed networks may soon increase the network bandwidth available to workstation class computers by two orders of magnitude. Combined with the dramatic increase in microprocessor speed, these technological advances make possible new kinds of applications, such as multimedia and parallel computing on networks of workstations.

At the same time, the operating system, in its role as mediator and multiplexor of computing resources, is threatening to become a bottleneck. The underlying cause is that main memory performance has not kept up with the growth of CPU and I/O speed, thus opening a bandwidth gap between CPU and main memory, while closing the old gap between main memory and I/O. Current operating systems fail to properly take into account the performance characteristics of the memory subsystem. The trend towards server-based operating systems exacerbates this problem, since a modular OS structure tends to increase pressure on the memory system.

This dissertation is concerned with the I/O bottleneck in operating systems, with particular focus on high-speed networking. We start by identifying the causes of this bottleneck, which are rooted in a mismatch of operating system behavior with the performance characteristics of modern computer hardware. Then, traditional approaches to supporting I/O in operating systems are re-evaluated in light of current hardware performance tradeoffs. This re-evaluation gives rise to a set of novel techniques that eliminate the I/O bottleneck.

## STATEMENT BY AUTHOR

This dissertation has been submitted in partial fulfillment of requirements for an advanced degree at The University of Arizona and is deposited in the University Library to be made available to borrowers under the rules of the Library.

Brief quotations from this dissertation are allowable without special permission, provided that accurate acknowledgment of source is made. Requests for permission for extended quotation from or reproduction of this manuscript in whole or in part may be granted by the copyright holder.

SIGNED:

## ACKNOWLEDGMENTS

First and foremost, I wish to thank Larry Peterson. He has been the ideal advisor, one who allowed me to pursue my own directions, while providing me with the optimism, experience and insight I often lacked. I owe thanks to Norm Hutchinson for his support and the many exciting debates we had during and after his time at Arizona. Thanks also to my other committee members, Rick Schlichting and Greg Andrews, for their support and encouragement.

The entire Computer Science department at Arizona deserves credit for creating and maintaining a superb environment in which to work and be productive. Special thanks to Cara Wallace and Margaret Newman for their patience, to Jana Zeff for getting me into the program six years ago, and to Wendy Swartz for helping me get out. I will miss the many enlightening discussions and Kippy's luncheons with Mark Abbott, Lawrence Brakmo, David Mosberger, Erich Nahum, Sean O'Malley, Michael Pagels, and Charlie Turner.

I am thankful to Bruce Davie and Bellcore for making the OSIRIS boards available to me, and for the opportunity to engage in a fruitful and pleasant research cooperation. Special thanks to Bruce for his support and all the fun we had.

As the real brain behind this work, my cat Nene deserves special consideration. His help with GigaMetrics was indispensable.

This work was supported by the National Science Foundation under Grant CCR-9102040, by ARPA under Contract DABT63-91-C-0030, and by Sun Microsystems, Inc.

# TABLE OF CONTENTS

| ABSTRACT                                               |    |  |  |  |  |  |  |  |

|--------------------------------------------------------|----|--|--|--|--|--|--|--|

| CHAPTER 1: Introduction                                |    |  |  |  |  |  |  |  |

| 1.1 The Memory Bandwidth Bottleneck                    |    |  |  |  |  |  |  |  |

| 1.2 Server-Based Operating System Structure            |    |  |  |  |  |  |  |  |

| 1.3 Thesis Statement and Contributions                 |    |  |  |  |  |  |  |  |

| 1.4 Dissertation Overview                              |    |  |  |  |  |  |  |  |

| CHAPTER 2: The Operating System I/O Bottleneck         | 21 |  |  |  |  |  |  |  |

| 2.1 Memory Performance                                 |    |  |  |  |  |  |  |  |

| 2.2 Effectiveness of Cache Memories                    | 23 |  |  |  |  |  |  |  |

| 2.3 Avoiding Main Memory Traffic                       |    |  |  |  |  |  |  |  |

| 2.3.1 Device–Memory Transfers                          | 25 |  |  |  |  |  |  |  |

| 2.3.2 Cross-Domain Data Transfers                      |    |  |  |  |  |  |  |  |

| 2.3.3 Data Manipulations                               | 27 |  |  |  |  |  |  |  |

| 2.3.4 Buffer Management                                | 28 |  |  |  |  |  |  |  |

| 2.3.5 Application Programming Interface                |    |  |  |  |  |  |  |  |

| 2.4 End-to-End Design                                  | 29 |  |  |  |  |  |  |  |

| 2.4.1 Hardware Streaming                               |    |  |  |  |  |  |  |  |

| 2.4.2 DMA-DMA Streaming                                | 31 |  |  |  |  |  |  |  |

| 2.4.3 OS Kernel Streaming                              |    |  |  |  |  |  |  |  |

| 2.4.4 User-Level Streaming                             |    |  |  |  |  |  |  |  |

| 2.4.5 Need for Integration                             |    |  |  |  |  |  |  |  |

| 2.5 A Buffer Abstraction for an Integrated Data Path   |    |  |  |  |  |  |  |  |

| 2.5.1 The IOData Abstract Data Type                    |    |  |  |  |  |  |  |  |

| 2.5.2 Implementation                                   |    |  |  |  |  |  |  |  |

| 2.6 Concluding Remarks                                 |    |  |  |  |  |  |  |  |

| CHAPTER 3: OS Support for a High-Speed Network Adaptor | 37 |  |  |  |  |  |  |  |

| 3.1 Experimental Hardware and Software                 |    |  |  |  |  |  |  |  |

| 3.2 Host/Board Communication                           |    |  |  |  |  |  |  |  |

| 3.2.1 Shared Data Structure                            |    |  |  |  |  |  |  |  |

| 3.2.2 Interrupts                                       |    |  |  |  |  |  |  |  |

| 3.3 Physical Buffer Fragmentation                      |    |  |  |  |  |  |  |  |

| 3.4 Cache Coherence                                    |    |  |  |  |  |  |  |  |

| 3.5 Page Wiring                                        |    |  |  |  |  |  |  |  |

| 3.6 DMA Length                                         |    |  |  |  |  |  |  |  |

| 3.7        | DMA ve         | ersus PIO                                                      |

|------------|----------------|----------------------------------------------------------------|

| 3.8        | New OS         | Mechanisms                                                     |

|            | 3.8.1          | Fast Buffers                                                   |

|            | 3.8.2          | Application Device Channels                                    |

| 3.9        | Perform        | ance                                                           |

| 3.10       | Conclud        | ing Remarks                                                    |

|            |                |                                                                |

|            |                | ecoupling Modularity and Protection                            |

| 4.1        |                | ion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $53$ |

|            | 4.1.1          | Why Separate Modularity and Protection?                        |

|            | 4.1.2          | How To Separate Modularity and Protection                      |

| 4.2        |                | ctural Model                                                   |

| 4.3        |                | Invocation Mechanism                                           |

|            | 4.3.1          | Design Issues                                                  |

|            | 4.3.2          | Object References and Local Invocation                         |

|            | 4.3.3          | Non-Local Invocation                                           |

| 4.4        |                | ance                                                           |

| 4.5        |                | on                                                             |

|            | 4.5.1          | Modularity and Protection                                      |

|            | 4.5.2          | Interface design                                               |

|            | 4.5.3          | Object Systems                                                 |

| 4.6        | Related        | work                                                           |

| 4.7        | Conclud        | ing Remarks                                                    |

| CHAPT      | ER 5: H        | igh-Bandwidth Cross-Domain Data Transfer                       |

| 5.1        | Motivat        |                                                                |

| 5.2        |                | erizing Network I/O                                            |

| 0.2        | 5.2.1          | Networks and Buffers                                           |

|            | 5.2.2          | Allocating Buffers                                             |

|            | 5.2.2          | Accessing Buffers                                              |

|            | 5.2.4          | Summary of Requirements                                        |

| 5.3        | -              | Work                                                           |

| 0.0        | 5.3.1          | Page Remapping                                                 |

|            | 5.3.2          | Shared Memory                                                  |

| 5.4        | Design         |                                                                |

| 0.1        | 5.4.1          | Basic Mechanism                                                |

|            | 5.4.2          | Optimizations                                                  |

| 5.5        |                | entation                                                       |

| 0.0        | 5.5.1          | Allocation                                                     |

|            | 5.5.1<br>5.5.2 | Transfer  81    82                                             |

|            | 5.5.2<br>5.5.3 | Italisier                                                      |

|            | 5.5.3          | Domain Termination                                             |

|            | 5.5.4<br>5.5.5 |                                                                |

| 56         |                | 1                                                              |

| 5.6<br>5.7 |                |                                                                |

| ə.(        | DISCUSSI       | on                                                             |

|       | 5.7.1 How Many Domains?                        | 89   |

|-------|------------------------------------------------|------|

|       | 5.7.2 Characteristics of Network I/O Revisited | 89   |

|       | 5.7.3 Architectural Considerations             | 90   |

|       | 5.7.4 Relationship to Other VM Systems         | 91   |

| 5.8   | Concluding Remarks                             | 91   |

| СНАРТ | ER 6: Application Device Channels              | 93   |

| 6.1   | Motivation                                     | 93   |

| 6.2   | Design                                         | 94   |

| 6.3   | Implementation                                 | 96   |

| 6.4   | Related Work                                   | 97   |

| 6.5   | Performance                                    | 97   |

| 6.6   | Summary                                        | 98   |

| СНАРТ | ER 7: Conclusion                               | 99   |

| 7.1   | Contributions and Limitations                  | . 99 |

| 7.2   | Future Directions                              | 100  |

| REFER | ENCES                                          | 101  |

# LIST OF FIGURES

| 1.1 | Block Diagram of a DEC 3000/600 AXP                                |

|-----|--------------------------------------------------------------------|

| 2.1 | Implementation of Messages in the <i>x</i> -kernel                 |

| 2.2 | Various Forms of Data Streaming                                    |

| 2.3 | Dependencies among copy-avoiding techniques                        |

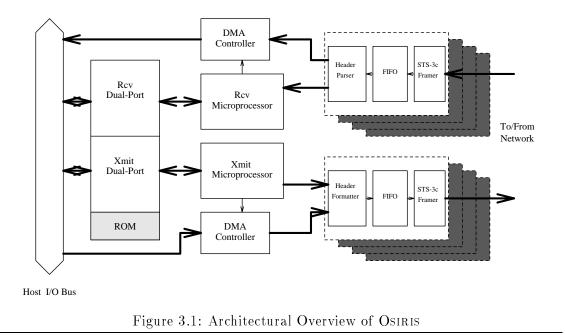

| 3.1 | Architectural Overview of Osiris                                   |

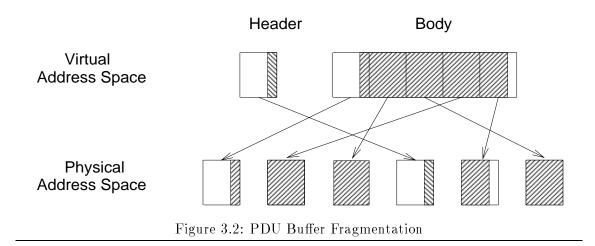

| 3.2 | PDU Buffer Fragmentation 42                                        |

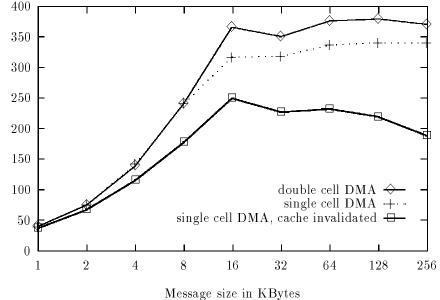

| 3.3 | DEC 5000/200 UDP/IP/OSIRIS Receive Side Throughput                 |

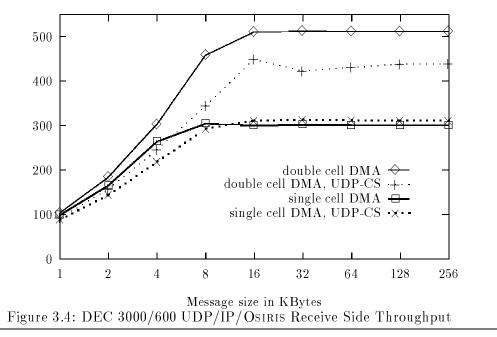

| 3.4 | DEC 3000/600 UDP/IP/OSIRIS Receive Side Throughput 50              |

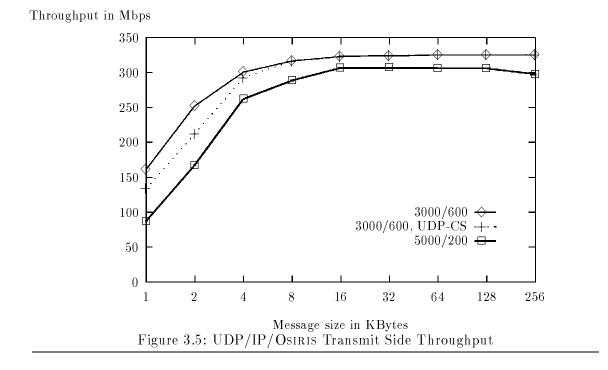

| 3.5 | UDP/IP/OSIRIS Transmit Side Throughput 51                          |

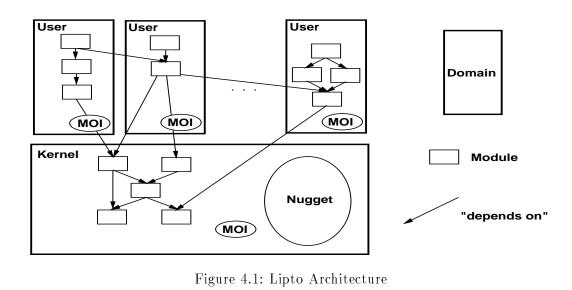

| 4.1 | Lipto Architecture                                                 |

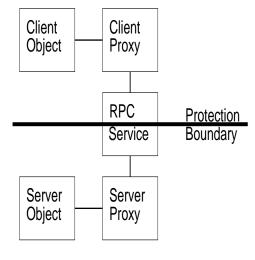

| 4.2 | Proxy Objects and RPC 61                                           |

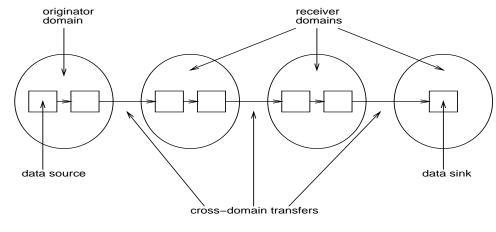

| 5.1 | Layers Distributed over Multiple Protection Domains                |

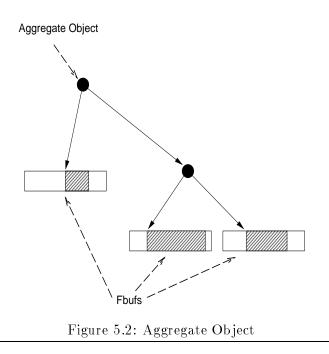

| 5.2 | Aggregate Object                                                   |

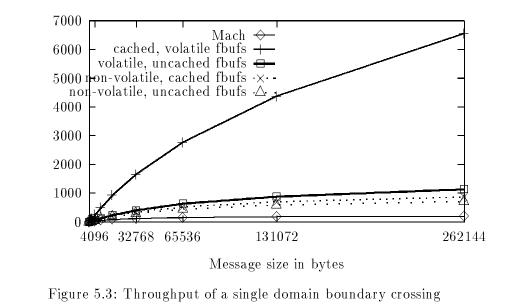

| 5.3 | Throughput of a single domain boundary crossing                    |

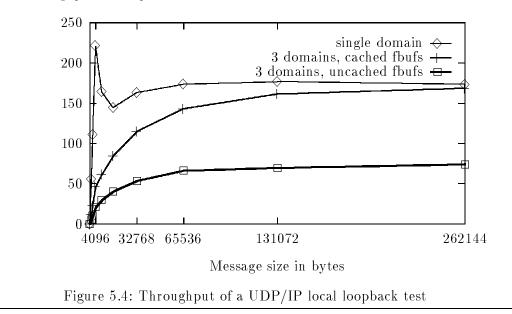

| 5.4 | Throughput of a UDP/IP local loopback test                         |

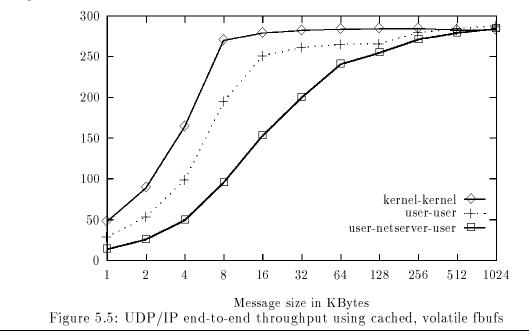

| 5.5 | UDP/IP end-to-end throughput using cached, volatile fbufs          |

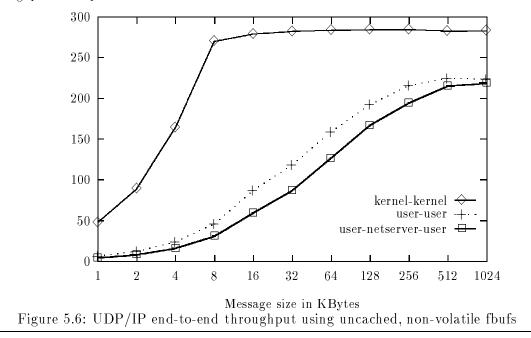

| 5.6 | UDP/IP end-to-end throughput using uncached, non-volatile fbufs 88 |

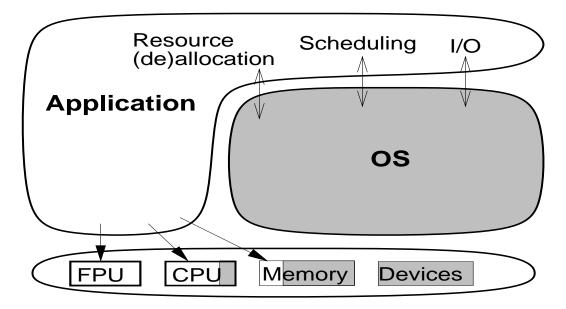

| 6.1 | Application-OS-Hardware Interaction                                |

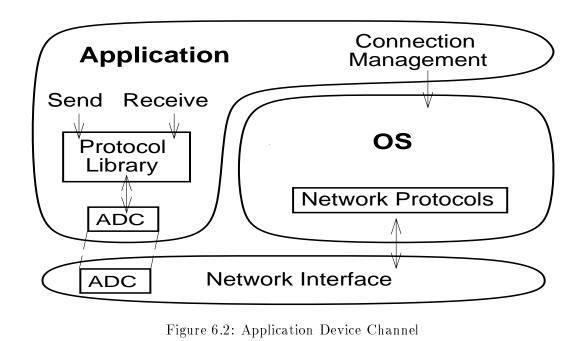

| 6.2 | Application Device Channel                                         |

### ABSTRACT

The advent of high-speed networks may soon increase the network bandwidth available to workstation class computers by two orders of magnitude. Combined with the dramatic increase in microprocessor speed, these technological advances make possible new kinds of applications, such as multimedia and parallel computing on networks of workstations.

At the same time, the operating system, in its role as mediator and multiplexor of computing resources, is threatening to become a bottleneck. The underlying cause is that main memory performance has not kept up with the growth of CPU and I/O speed, thus opening a bandwidth gap between CPU and main memory, while closing the old gap between main memory and I/O. Current operating systems fail to properly take into account the performance characteristics of the memory subsystem. The trend towards server-based operating systems exacerbates this problem, since a modular OS structure tends to increase pressure on the memory system.

This dissertation is concerned with the I/O bottleneck in operating systems, with particular focus on high-speed networking. We start by identifying the causes of this bottleneck, which are rooted in a mismatch of operating system behavior with the performance characteristics of modern computer hardware. Then, traditional approaches to supporting I/O in operating systems are re-evaluated in light of current hardware performance tradeoffs. This re-evaluation gives rise to a set of novel techniques that eliminate the I/O bottleneck.

# CHAPTER 1 Introduction

Emerging network technologies such as fiber-optic transmission facilities and Asynchronous Transfer Mode (ATM) hold the promise of delivering data rates approaching 1 Gb/s between individual workstations on local and wide-area networks<sup>1</sup> [IEE90, C<sup>+</sup>93b]. This order-of-magnitude increase in network capacity, combined with the explosive growth in microprocessor performance, will enable a range of innovative new applications of distributed computing. Distributed multimedia, including real-time audio and video, and supercomputing on clusters of workstations are examples of such emerging applications. One important factor that could dramatically influence the success of these new technologies is the degree to which operating systems can make these networking resources available to application programs.

The role of an operating system (OS) is to mediate and multiplex the access of multiple application programs to the computing resources provided by the underlying hardware. Ideally, the operating system should not itself consume a significant share of these resources. Unfortunately, current operating systems are threatening to become the bottleneck in delivering input/output (I/O) data streams to application programs at high rates [CT90, DWB<sup>+</sup>93, ST93, Ram93]. In particular, data streams between applications on hosts connected by high speed networks suffer bandwidth degradation and added latency due to the operating system running on the hosts.

This dissertation is concerned with the I/O bottleneck in operating systems, with particular focus on high-speed networking. We start by identifying the causes of this bottleneck, which are rooted in a mismatch of operating system behavior with the performance characteristics of modern computer hardware. Then, traditional approaches to supporting I/O in operating systems are re-evaluated in light of current hardware performance tradeoffs. This re-evaluation gives rise to a set of novel techniques that eliminate the I/O bottleneck.

## 1.1 The Memory Bandwidth Bottleneck

The root cause of the OS I/O bottleneck is that speed improvements of main memory have lagged behind those of the central processing unit (CPU) and I/O devices during the past decade [CW92, HP90]. In state-of-the-art computer systems, the bandwidth of main memory is orders of magnitude lower than the bandwidth of the CPU, and the bandwidths of the fastest I/O devices approach that of main memory<sup>2</sup>. The previously

<sup>&</sup>lt;sup>1</sup>Throughout this work, we use the convention that 1 Gb and 1 Mb equals  $10^9$  and  $10^6$  bits, respectively, and 1 MB =  $2^{20}$  bytes.

$<sup>^{2}</sup>$ We define CPU bandwidth as the maximal sustained rate, in bytes per second, at which the CPU can absorb data; memory bandwidth as the sustained rate at which the CPU can read data from main memory; and the I/O bandwidth as the sustained rate at which data can be transferred to and from I/O

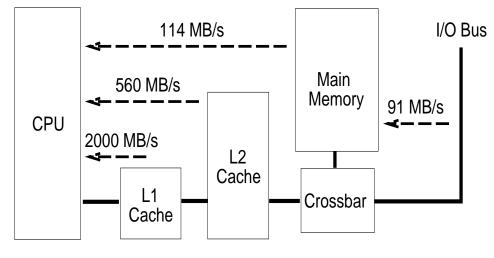

Figure 1.1: Block Diagram of a DEC 3000/600 AXP

existing gap between memory and I/O bandwidth has almost closed, and a wide gap has opened between CPU and memory bandwidth, leaving memory as a potential bottleneck.

To bridge the gap between CPU and memory speed in modern computers, system designers employ sophisticated *cache* systems. A cache exploits *locality of reference* in memory accesses to reduce main memory traffic. Locality of reference is the property of a sequence of memory accesses to reference preferentially those memory locations that were either accessed recently (temporal locality), or that are close to recently accessed locations in the address space (spatial locality). A cache is a high-speed memory that holds a recently accessed subset of the data stored in main memory. When the CPU accesses a main memory location for which the cache holds a copy, no main memory access is necessary, and the operation can complete at the speed of the cache memory. A cache reduces main memory traffic and lowers the average memory access latency experienced by the CPU. The effectiveness of the cache in bridging the CPU/memory speed gap depends on the degree of locality in the memory accesses of the executed program.

Figure 1.1 depicts the block diagram of a DEC 3000/600 AXP system. The performance characteristics of this machine are typical of currently available high-end desktop workstations. Observe that the available bandwidth on the path between CPU and main memory is less than twice the bandwidth of the I/O bus. Thus, in order to deliver the bandwidth of a high speed I/O device to an application that consumes the data, care must be taken to ensure that the data does not travel the data path between the cache and main memory more than once. Stated differently, a desirable scenario is one in which the data received from a fast input device is brought into the cache once and remains there until it is consumed. The cache system can achieve this scenario, as long as the set of CPU accesses to the data have sufficient locality, relative to the size and associativity of the cache.

Unfortunately, in most current systems the accesses to I/O data buffers generated by

devices.

operating system and applications *do not* have sufficient locality to allow the cache system to minimize memory traffic. As a result, excess memory traffic is causing a substantial drop in I/O performance, i.e., throughput and latency. This poor locality is caused by

- data movements (copying),

- inappropriate scheduling of the various I/O processing steps, and

- a system structure that requires OS kernel involvement in all I/O activity.

Moving or copying data from one main memory location to another causes poor access locality and thus increased memory traffic. Unnecessary data copying occurs in current systems due to a lack of integration in the design of I/O adaptors, buffer management schemes, interfaces, and mechanisms for the transfer of data across protection domain boundaries.

Locality can suffer further because various I/O processing steps and their associated data accesses occur in the context of multiple, separately scheduled threads of control (e.g., interrupt handlers, kernel threads, application processes). In a multiprogrammed environment, these processing steps may not be scheduled to execute in strict succession. That is, the processing steps of a data unit may be interleaved with the execution of unrelated tasks, with their own and distinct set of memory references. Thus, accesses to a particular I/O data unit are temporally separated, resulting in poor data access locality<sup>3</sup>.

Finally, current systems require that the operating system kernel be involved in each individual I/O operation that an application initiates. Thus, I/O requires a processor reallocation to switch between application and operating system, and the transfer of data across the user/kernel protection boundary. Both entail a drop in memory access locality, which can limit I/O bandwidth and significantly contribute to I/O latency.

In summary, limited memory bandwidth in modern computer systems is a potential source of performance problems. Cache systems can hide the slow speed of main memory only when the memory accesses generated by a program have good locality of reference. Accesses to I/O data generated by operating systems and applications tend to have poor locality, rendering the cache ineffective in avoiding the memory bottleneck in processing network I/O.

## **1.2** Server-Based Operating System Structure

The problem of poor memory access locality during I/O operations is aggravated by the recent trend in operating system design towards a modular structure, where different parts of the operating system reside in separate protection domains [ABB+86, RAA+88, Hil92]. In these systems, I/O requests and associated data may have to cross additional protection boundaries and scheduling points between application programs and I/O devices. Studies have shown that reduced memory access locality in these systems has a negative impact on overall system performance [CB93], and can have a strong impact on networking performance [MB93b].

<sup>&</sup>lt;sup>3</sup>An additional problem can occur on shared memory multiprocessors, when not all processing steps are scheduled to run on the same processor.

Thus, operating system designers are facing a dilemma. Growing concern for ease of distribution, validation, configuration, and maintenance in the face of increasingly complex operating systems strongly suggests more modular architectures, such as microkernelbased (server based) systems. On the other hand, server-based operating systems appear to make it even more difficult to achieve high-performance I/O than the traditional, monolithically structured systems.

## **1.3** Thesis Statement and Contributions

The hypothesis of this dissertation is that the I/O bottleneck in current operating systems is caused by the lack of a coordinated design of OS software and device adaptor hardware that minimizes main memory traffic. This coordinated design must encompass the entire I/O data path, from application programming interfaces (API), to OS architecture, OS facilities for buffer management and data transfer across protection boundaries, to I/O device adaptors.

The goal of this dissertation is to remove the I/O bottleneck, without sacrificing modularity in the structure of operating system and applications. Towards this goal, the contributions here are a set of novel techniques that are part of a coordinated design to minimize main memory traffic:

- A new structuring approach for operating systems that allows fine-grained modularity without the performance penalty of an equally fine-grained protection structure;

- a new OS facility for the management and transfer of I/O data buffers across protection domain boundaries;

- a new OS facility that allows applications to bypass the OS kernel in common I/O operations, while leaving control over the device in the hands of the operating system; and

- a set of techniques that reduce host processing overhead and achieve high performance in driving a high-speed network adaptor.

These new techniques result from a re-evaluation of traditional approaches to supporting I/O in operating systems. In particular, they are based on the following key observations.

- Memory bandwidth is a scarce resource. The traditional approach to performanceoriented system design is to focus on minimizing the number of CPU instructions executed during an operation. The characteristics of modern computer systems with their fast CPUs, limited memory bandwidth, and fast I/O devices make it necessary to focus instead on minimizing main memory traffic.

- **Communication is a common operation.** Current operating system designs require OS kernel involvement in each I/O operation. This approach is well suited for applications that spend most of their time operating on data stored in main memory, and that perform occasional, coarse-grained I/O operations. The kinds of distributed applications that are enabled by high-speed networking are likely to perform frequent,

fine-grained I/O, making communication a common operation. Thus, operating systems should be optimized accordingly and should implement common I/O operations without requiring kernel involvement.

This dissertation focuses on the primary problem of preserving the bandwidth and latency of high-speed networks at the application level. The advent of high-speed networking and the applications that it enables also pose a number of secondary problems. For example, live audio and video applications require that the operating system schedules resources in such a way that the real-time constraints of continuous media are met. This issue is not addressed here, but is receiving attention by a host of other researchers [AH91, JH93, Jef92, RR93, LKG92].

## 1.4 Dissertation Overview

Chapter 2 reviews the relevant performance characteristics of modern computer systems (i.e., memory and cache behavior) in more detail. It describes the various causes of excess memory traffic in current systems and discusses techniques found in the literature to avoid these inefficiencies. We show that theses techniques, when applied naively, can fail to reduce memory traffic significantly. Instead, it is necessary to coordinate their application as part of an end-to-end design. The chapter concludes by proposing an abstract data type that encapsulates I/O data buffers along the entire data path through a host system. This abstract data type can serve as the centerpiece of a coordinated design for an efficient I/O data path.

We begin Chapter 3 by describing the experimental hardware and software platforms used in the research that led to this dissertation. Then, we report on a number of low-level performance problems that were encountered in driving a very high speed network adaptor connected to a modern workstation, and we present novel techniques to deal with the problems. The chapter concludes with a detailed performance study of network performance achieved between pairs of workstations connected by an experimental 622 Mb/s fiber-optic network.

Chapter 4 presents a new approach to structuring an operating systems that affords fine-grained modularity without the performance cost of an equally fine-grained protection structure. In particular, this approach avoids the tradeoff between a modular OS architecture and high-performance I/O, which governs conventional server-based operating systems. The implementation of a prototype kernel based on this approach is described, and a performance study is presented.

In Chapter 5 we present a novel OS facility, called *fast buffers* (fbufs), for the management and transfer of I/O data buffers across protection domains boundaries, both in monolithic and server-based operating systems. The design and implementation of this facility is described in detail. A performance study shows that fbufs allow the transfer of large network messages across multiple protection domain boundaries without a loss in throughput.

Chapter 6 introduces an innovative OS facility that takes advantage of user-level network protocols and limited support from the network adaptor. It gives applications direct but controlled access to the network adaptor, which significantly reduces network message latency. This facility, called *application device channels* (ADCs), leaves control of the network adaptor in the hands of the operating system, thus allowing transparent sharing of the device among multiple, non-privileged application programs.

Finally, Chapter 7 summarizes the contributions, points out limitations, and identifies future directions of research.

# CHAPTER 2 The Operating System I/O Bottleneck

This chapter presents an overview of the hardware and software issues relevant to I/O performance in operating systems. We show that the memory bandwidth of modern, general-purpose computer systems is within the same order of magnitude as the bandwidth of emerging high-speed networks. Furthermore, we present evidence that this situation will persist for the foreseeable future, because cost considerations prevent the use of dramatically faster main memory and interconnect technology in this class of machine. As a consequence, operating systems must be designed to minimize main memory traffic that results from network and other I/O activity. Specifically, the number of trips that network data takes across the CPU-memory data path must be minimized in order to avoid a bottleneck.

We proceed to survey several techniques from the literature that can be applied to this problem. An important lesson we learn from this survey is that naively applying these techniques is not sufficient for achieving good application-to-application throughput. Instead, it is necessary to integrate the entire data path, from a source device, through the operating system, application programs, and possibly to a sink device. The chapter concludes by outlining a fully integrated data path that optimizes end-to-end throughput.

Throughout this chapter, we include in our analysis the most general case of a microkernel-based system, where device drivers, network protocols, and application software all potentially reside in different protection domains. This consideration is well justified in light of the advantages of server-based systems (e.g., configurability, distributability, portability, and so on), as well as the recent trend towards such systems in commercial offerings.

## 2.1 Memory Performance

This section analyzes the performance of main memory in modern, general-purpose computer systems. We present measurements of main memory bandwidth in several commercially available desktop workstations, and discuss the constraints for designer of main memory subsystems. The conclusion is that main memory bandwidth is likely to remain within the same order of magnitude as I/O bandwidth for the foreseeable future.

Table 2.1 shows, for each of four desktop workstations, the results of several memory bandwidth measurements described below. The CPU/Memory bandwidth numbers reported were obtained using a simple benchmark that measures the sustained bandwidth during a series of read, write, and copy operations. The benchmark was coded in C. No attempt was made to tune the program for a particular machine. The C code was compiled in each case with two different compilers; the vendor's compiler, and the GNU project's gcc compiler [Sta93]. All appropriate compiler optimizations were turned on.

|                           | MB/s, sustained |         |          |

|---------------------------|-----------------|---------|----------|

|                           | Сору            | Read    | Write    |

| IBM $RS/6000$ 340         | 51              | 81      | 73       |

| Sun SS10/41               | 26              | 42      | 39       |

| HP $9000/735$             | 31              | 71      | 52       |

| DEC $3000/600$            | 52              | 109     | 111      |

| Table 2.1: CPU-Memory Bar | ndwidth         | of seve | ral Worl |

The read and write columns were measured by reading (writing) each element of an array. The copy column was measured using two methods: Element-wise assignment of two arrays, and invoking the bcopy() library function. The benchmark used arrays of type int (32bits) and double (64bits). The numbers reported are the best that could be achieved in each case; i.e., GNU compiler versus vendor's compiler, int versus double for the read and write columns, and int versus double versus bcopy() for the copy column. Finally, the size and alignment of the arrays was chosen to eliminate effects of the data cache.

The main result is that the measured memory bandwidths of current workstation is on the order of 100 MB/s. Note that somewhat better results could likely be obtained using machine-specific, hand-optimized machine code, since the compiler-generated machine code, and the vendor-provided implementation of the bcopy() function may be less than optimal for the intended task of the benchmark program. We have deliberately not tried to eliminate this factor, since it equally affects real programs. An inspection of the generated code for some of the machines convinced us that bandwidth improvements with hand-optimized costs would not exceed 50%.

An experimental ATM high-speed network adaptor described in Chapter 3 can simultaneously transmit and receive on a pair of 622 Mb/s fiber-optic links. Adjusting for ATM cell overhead, the adaptor can generate an aggregate I/O bandwidth of 134 MB/s. Clearly, the memory bandwidth of current workstation is within the same order of magnitude as the bandwidth of this network adaptor.

Network adaptors with such high bandwidth are not yet commercially available. One could conjecture that by the time such networks are on the market, main memory bandwidth will have improved to the point where it is no longer a bottleneck. In the following, we argue that main memory bandwidth in next generation workstations is not likely to enjoy order-of-magnitude increases in bandwidth.

Cost and density make Dynamic Random Access Memory (DRAM) the technology of choice for the main memory system in general-purpose computer systems. DRAM performance is mainly characterized by its access latency, i.e., the time it takes, once an address is presented to a DRAM chip, for the corresponding data to become available. While DRAM density has improved dramatically in recent years, access latency has improved at a rate of only 7% per year [HP90].

Data is transferred between cache and main memory using fixed sized cache blocks. The main memory bandwidth available to the CPU is bounded by the ratio of the cache block size and the time it takes to read or write a cache block. This time consists of the memory access latency, plus the transfer time for a cache block. No dramatic improvements in memory access latency can be expected in the near future, due to the slow speed improvements of DRAMs. Techniques exist to increase the transfer rate, but an increase in transfer rate alone cannot deliver major increases in memory bandwidth because latency would increasingly dominate the transfer time for a fixed sized cache block. Increases in data transfer rate must be combined with an increase in cache block size to be effective. Unfortunately, the cache block size cannot be increased arbitrarily without affecting the hit rate of the cache systems [Prz90].

Several recently announced components integrate some form of a cache with a dynamic RAM to reduce the average access latency [CW92]. These integrated second level caches use large cache lines and are connected to the DRAM using wide data paths. As for any cache, the hit rate of these components depends on locality of reference. As we shall discuss in Section 2.2, accesses to I/O data exhibit poor locality. Furthermore, it is unclear whether the industry will accept the higher cost of these components.

While substantial improvements in main memory bandwidth can be expected in generalpurpose computer systems, it is unlikely that these improvements will out-pace the increases in I/O bandwidth by an order of magnitude. Thus, we conclude that main memory bandwidth in this class of machines will remain within the same order of magnitude as network bandwidth for the foreseeable future.

## 2.2 Effectiveness of Cache Memories

Modern computer systems employ caches to bridge the gap between CPU and main memory speeds. The idea is to keep a recently accessed portion of the main memory's data in a fast memory. Whenever a data item referenced by the CPU is found in the cache, no main memory access is necessary and the operation can complete at the speed of the cache memory. A cache increases system performance by reducing the average access latency for data and instructions. It also reduces contention for main memory access between processor(s) and DMA-based I/O devices. The effectiveness of a cache depends on the size and organization of the cache, and on locality in the CPU's memory accesses.

In general, an application program that processes I/O data causes the CPU to load from—and possibly store to—memory every word of a data unit, potentially multiple times. (The next section identifies reasons why these data accesses might occur.) This section argues that data caches are not effective in eliminating the corresponding main memory accesses. For the sake of this argument, we limit our attention to accesses of the actual I/O data, and ignore references to CPU instructions and other data that occur during an application's processing. For emerging high-bandwidth applications such as continuous media, accesses to I/O data arguably account for a significant portion of total execution time. In any case, we have already shown that unless care is taken, the I/O data accesses alone can cause a bottleneck. Consider the following factors, ordered roughly according to importance.

**Processor Scheduling:** CPU scheduling may cause the execution of other programs to be interleaved with the processing of a data unit. By the time processing resumes, cached portions of the data unit have most likely been replaced. On a multiprocessor,

the processing may even be resumed by a different CPU with its own data cache. There are a number of situations where scheduling occurs during the processing of a data unit. When the data unit is passed on to another thread (i.e., queued), a processor must be scheduled to run that thread. Queuing typically occurs at the user/kernel boundary, in certain protocols, and between the device driver's interrupt handler and the top half of the driver. In the worst case, additional queuing may occur between protocol layers. Moreover, hardware interrupts and the events they signal trigger processor rescheduling.

**Cache Size:** Cache memories, particularly fast on-chip caches, are limited in size. In practice, their effective size is further reduced due to the limited associativity of direct-mapped and set-associative organizations [Prz90]. For data to remain cached during a data operation that involves loading every word and storing it in a different location, the cache must be at least twice the size of the data unit. In practice, cache size requirements are further increased by accesses to program variables during and between data manipulations.

**Cache Organization:** Caches that are virtually indexed and tagged do not require a virtual-to-physical address translation to access cached data. With this approach, cached data from virtually shared pages cannot remain valid across protection domain boundaries. In other words, data must be re-loaded after a switch into a different protection domain, even if the data buffers are shared between the domains. Physically tagged caches do not have this problem. They require, however, that a Translation Lookaside Buffer (TLB) entry be active for the page that contains the referenced data. Network data buffers tend to be scattered across memory pages, which increases the demand for TLB entries. The resulting contention for TLB entries can add substantial costs to the access of cached data [PDP93].

**Cache Write Policy:** Uniprocessor data caches often employ a write-through policy, meaning that every store operation requires a write to main memory. Write buffers are typically used with write-through caches to decouple the CPU from the timing of memory writes. However, many consecutive writes—such as would occur when reading and writing every word of a data unit—can cause the CPU to stall on store instructions.

To quantify the effectiveness of the data cache in handling network data, Pagels [PDP93] conducted experiments that measure the amount of network data resident in the cache after OS processing. This cache residency value is a measure of the potential benefit obtained by a user process due to the caching of network data, thereby avoiding CPU/memory transfers. It provides an upper bound on the effectiveness of the cache when network data is processed without copying. Both monolithic and microkernel-based operating systems are included in this study. The results obtained in these measurements confirm that caches are not effective in eliminating main memory traffic associated with the accesses of network data.

In summary, we have shown that the main memory bandwidth in modern, generalpurpose computer systems is within the same order of magnitude as the bandwidth of emerging high-speed I/O devices such as ATM network adaptors. In order to sustain the bandwidth of these I/O devices, it is critical to minimize the main memory traffic caused by the processing of I/O data. Furthermore, the cache systems used in modern computers to bridge the gap between CPU and memory speed are not effective in eliminating main memory traffic caused by accesses to network data.

## 2.3 Avoiding Main Memory Traffic

The two previous sections document our argument that the CPU-memory bandwidth of workstations is within the same order of magnitude as the network bandwidth, and that data caches cannot eliminate main memory traffic caused by the processing of network I/O. It follows, therefore, that in order to preserve the bandwidth on the data path from a network device through the OS and application, and possibly to a sink device (e.g., display), multiple accesses of the data stored in main memory must be avoided.

Each of the following subsections identifies a potential main memory access along this path, briefly describes one or more technique for efficiently handling or avoiding it, and discusses the assumptions and limitations of these techniques.

#### 2.3.1 Device–Memory Transfers

Data must be moved between main memory and network/device adaptors. The techniques most commonly used are Direct Memory Access (DMA) and Programmed Input/Output (PIO). DMA allows an I/O adaptor to transfer data directly from/to main memory, without involving the CPU. PIO requires the processor to transfer individual data words (typically 32 bits) between main memory and I/O adaptor in a programmed loop.

With DMA, it is generally possible to transfer large blocks of data in a single bus transaction, thereby achieving transfer rates close to the limits of main memory and I/O bus. The data transfer can proceed concurrently with activity by the processor(s), although contention for main memory access may induce processor stalls during periods of heavy DMA traffic. On the downside, DMA requires some complexity in the device adaptors. In many machines, data caches and main memory may not be coherent with respect to DMA transfers. That is, after a DMA transfer from an I/O adaptor to main memory (DMA write), the cache may contain stale data. Consequently, the appropriate portions of the data cache must be invalidated by system software. Conversely, a write-back cache may have to be explicitly flushed prior to a a DMA read operation.

With PIO, the CPU is occupied during transfers from/to a device. Only a small fraction of the peak I/O bandwidth is often achieved, for the following reasons. The adaptor's control and data ports can either be mapped as cacheable or non-cacheable memory locations. In the non-cacheable case, each load/store instruction results in a short (i.e., one machine word) I/O bus transaction, resulting in poor sustained bandwidth. In the cacheable case, I/O bus transfers occur at cache line length. The resulting bandwidth is improved, but may still be far below the peak I/O bandwidth. Moreover, it is again necessary to flush the data cache to maintain consistency with the adaptor's ports.

Nevertheless, there are situations where PIO can be preferable over DMA. First, computations on the data that occur in the kernel, such as checksum calculations, can sometimes be integrated with the PIO data movement, saving a main memory access. Second, after a programmed data movement from an I/O adaptor to main memory, the data is in the cache. This can result in reduced memory traffic if the data is accessed again while it remains in the cache.

A scatter-gather capability in DMA-based I/O adaptors is important for reducing memory traffic. Scattering allows an incoming data unit to be placed into multiple, noncontiguous portions of main memory. Gathering allows an outgoing data unit to be collected from multiple, non-contiguous buffers. Scatter-gather allows DMA transfer from/to non-contiguous physical page frames, which greatly simplifies physical memory management in the operating system, and helps avoid copying data into contiguous storage. With PIO, scatter-gather can be trivially implemented in software.

Network adaptors may support packet demultiplexing prior to data transfer to main memory, allowing filtering and selective placement of data units in memory. In the simplest case, the adaptor allows the host to peek at a network packet's header. The host makes the demultiplexing decision and initiates the data transfer to the appropriate location in main memory, using DMA or PIO. More elaborate adaptors such as the ones described in Chapter 3 and in [KC88, BPP92] can be programmed by the host CPU to recognize network packets by their headers, and place them into appropriate memory locations using DMA without host intervention. This feature proves to be very useful in enabling OS facilities that can reduce main memory traffic (see Chapters 5 and 6).

#### 2.3.2 Cross-Domain Data Transfers

Protection in operating systems necessitates the transfer of data across protection domain (address space) boundaries. In the simplest case, an I/O data stream is used by a single application process running on top of a conventional monolithic operating system kernel. Here, I/O data must cross a single user/kernel boundary. In general, additional user processes, such as window managers and multimedia servers, and the OS servers of micro-kernel-based operating systems, may introduce additional domain boundary crossings into the I/O data path.

Software data copying as a means of transferring data across domain boundaries exacerbates the memory bottleneck problem. A number of techniques exist that rely on the virtual memory system to provide copy-free cross-domain data transfer. Virtual page remapping [Che88, TA91] unmaps the pages containing data units from the sending domain and maps them into the receiving domain. With Virtual copying (copy on write) [FR86], the sending and receiving domain share a single copy of the transferred pages, and physical copying occurs only when one of the domains attempts to modify the shared data unit. Shared virtual memory [SB90] employs buffers that are statically shared among two or more domains to avoid data transfers.

Virtual page remapping has *move* rather than *copy* semantics, which limits its utility to situations where the sender needs no further access to the transferred data. Virtual copying has copy semantics, but it can only avoid physical copying when the data is not written by either the sender or the receiver after the transfer. Both techniques require careful implementation to achieve low latency. The time it takes to switch to supervisor mode, acquire necessary locks to VM data structures, change VM mappings—perhaps at several levels—for each page, perform TLB/cache consistency actions, and return to user mode poses a limit to the achievable performance. Measurements we performed on a DecStation 5000/200 suggest that page remapping is not fast enough to sustain the bandwidth of a high-speed network adaptor (see Section 5.3.1).

Another complication arises from the fact that both techniques work at the granularity of the VM page size. A mismatch between data unit size and VM page size implies that a portion of the last page overlapped by the data unit will remain unused. For reasons of data privacy, the kernel must clear (e.g., fill with zeroes) this portion of a newly allocated buffer page, which can incur a substantial cost, relative to the overall overhead of buffer management and cross-domain data transfer. A similar problem occurs if headers at the front of a received network packet contain sensitive data that must be hidden from user processes. The partial use of memory pages also requires more pages per amount of network data, resulting in increased physical memory consumption, page allocation and remap overhead, and demand for TLB entries.

Shared virtual memory avoids data transfer and its associated costs altogether. However, its use may compromise protection and security between the sharing protection domains. Since sharing is static—a particular page is always accessible in the same set of domains—a priori knowledge of all the recipients of a data unit is required. A novel technique, called *fbufs* (introduced in Chapter 5), combines page remapping with shared virtual memory, and exploits locality in network traffic to overcome some of the shortcomings of either technique.

#### 2.3.3 Data Manipulations

Data manipulations are computations that inspect and possibly modify every word of data in a network data unit. Examples include encryption, compression, error detection/correction, presentation conversion, and application-specific computations. Data manipulations can be performed in hardware or software. Hardware support for data manipulations can reduce CPU load, and when properly integrated, reduce memory traffic. For certain manipulations like video (de)compression, hardware support may be necessary in the short term, due to the computational complexity of the task. To rely on hardware for all data manipulations, however, seems too constraining for innovative high-bandwidth applications.

Software data manipulations typically access the data independently from each other since they are generally part of distinct program modules that reside in separate protection domains (OS kernel, servers, application). The resulting memory references have poor locality, and thus require that data be loaded from (and possibly stored back to) main memory. The slow main memory accesses contribute significantly to the time required to complete the data manipulation, and thus limit the bandwidth.

Memory references resulting from data manipulations can be minimized through Integrated Layer Processing (ILP) [CT90, AP93]. ILP is a technique for implementing communication software that avoids repeated memory reference when several data manipulations are performed. The data manipulation steps from different protocol implementations are combined into a pipeline. A word of data is loaded into a register, then manipulated by multiple data manipulation stages while it remains in a register, then finally stored—all before the next word of data is processed. In this way, a combined series of data manipulations only references memory once, instead of potentially accessing memory once per distinct layer.

A detailed performance study demonstrates that integration can have a significant impact on performance [AP93]. On the other hand, a major limitation of ILP is that data manipulations performed by program modules in different protection domains cannot be

easily integrated.

#### 2.3.4 Buffer Management

Buffer editing—which we distinguish from data manipulations that require the inspection and/or modification of each word of data—can be expressed as a combination of operations to create, share, clip, split, concatenate, and destroy buffers. When naively implemented, these operations may require physical copying of the buffers.

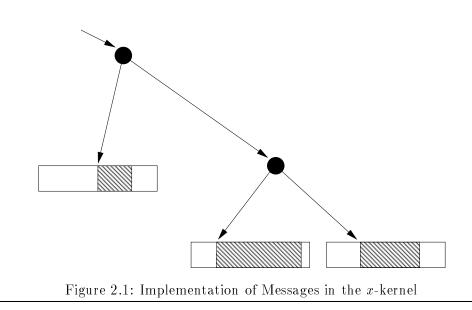

A buffer manager that employs lazy evaluation of buffers to implement the aforementioned primitives can facilitate copy-free buffer editing. The manager provides an abstract data type that represents the abstraction of a single, contiguous buffer. An instance of this abstract buffer type might be stored in memory as a sequence of not necessarily contiguous fragments. For example, the x-kernel [HP91] represents messages by a directed acyclic graph (DAG), where the leaves correspond to buffers, and the leftmost leaf can have information (e.g., headers) prepended to the front. Figure 2.1 depicts x-kernel messages.

Since buffer editing occurs frequently in network protocol implementations, buffer managers are used in the network subsystem of many operating systems. The scope of these managers is restricted to a single protection domain, typically the kernel. In most systems, a software copy into a contiguous buffer is necessary when a data unit crosses a protection domain boundary.

#### 2.3.5 Application Programming Interface

The application programming interface (API) defines the services and operations that an operating system provides to application programs. In particular, it defines the syntax and semantics of the operations (system calls) exported by the OS. I/O data buffers appear in this definition as arguments to I/O operations. The argument passing semantics for the I/O operations defined by this interface can have a significant impact on the efficiency of I/O data transfers between OS kernel and applications.

Consider, for example, the UNIX read() and write() system calls [UNI89]. These operations specify a pointer argument that refers to the address of a contiguous buffer in the application's address space, and an integer argument that represents the size of the buffer. Application programs may choose an address anywhere within their populated address space, with no restrictions on the size and alignment of the buffer. The semantics of these operations specify that data is *copied* from and to the application buffer during the operation. That is, during a read system call, the application buffer is overwritten with the input data. After a write operation completes, it is assumed that output data has been copied from the application buffer, and the application is free to reuse (modify) the buffer.

The low-level representation of data buffers and the semantics of the read and write operations make it difficult for an implementation to avoid physical copying of data. First, all virtual memory (VM) based techniques for cross-domain data transfer operate at the granularity of a VM page. If the user buffer's first and last addresses are not page aligned, the system must copy portions of the first and last page overlapped by the buffer. Depending on the length of the user buffer, the portion of a buffer that must be copied can be significant. Second, the semantics of the write system call permit the user process to modify (reuse) the user buffer immediately after the call returns. If this happens, the system must either copy the affected page after all, or block the user process until the operating system is done with the output data. The latter approach may degrade the application's effective I/O bandwidth even though it avoids copying, because it prevents overlapping of I/O and application processing. Third, the read and write system calls specify a single, contiguous data buffer. Data that arrives from a network device is often scattered in main memory, due to the reassembly of fragmented network packets. If a read operation specifies an amount of data that spans several fragments, copying of data is unavoidable.

In summary, there are three problems with the UNIX read and write system calls, as they relate to avoiding data copying. They allow data buffers with arbitrary alignment and length, they require contiguous data buffers, and they have copy semantics. A proposal for an API that lends itself to efficient data transfer is presented in Section 2.5.

## 2.4 End-to-End Design

This section gives an overview of the design space for an I/O subsystem that minimizes main memory traffic along the entire data path from source to sink device. We focus on several representative sample points in the design space. For each sample point, we discuss tradeoffs, determine the optimal data path, and select appropriate implementation techniques to achieve the optimal data path.

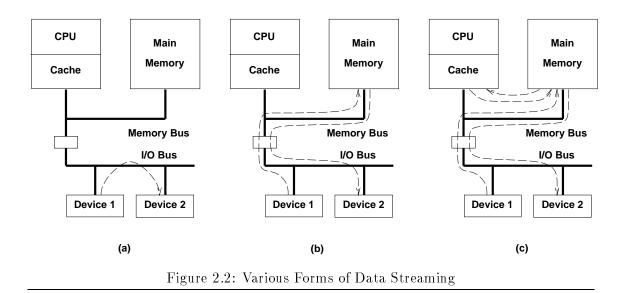

Throughout this section, we refer to the block diagrams in Figure 2.2 to depict the data flow from source to sink device. In the architectural model underlying these diagrams, CPU and cache are connected to main memory using a dedicated memory bus. A bus converter ties the memory bus to a separate I/O bus, to which all devices are attached.

#### 2.4.1 Hardware Streaming

One approach to avoiding the main memory bottleneck is to remove both the CPU and main memory from the data path. The data path is set up and controlled by software, but the data itself is transferred directly from source to sink device, bypassing main memory (Figure 2.2, (a)). Both device adaptors and the I/O bus must support peer-to-peer transfers, and the adaptors must be able to perform demultiplexing and any necessary data format conversions.

This method can be characterized by a lack of integration with the host computer system. Since application programs have no access to the data, they are constrained by the functionality provided by the adaptor boards. The result is a tradeoff between complexity in the device adaptors on one hand, and flexibility and functionality on the other.

Adaptors that support a fixed set of capabilities offer little room for innovation to applications. An alternative is for the adaptor to provide components that can be programmed by applications. This can take the form of special-purpose processors, or programmable circuitry. Unfortunately, this approach has problems of its own. First, it is difficult for applications to use programmable device adaptors in a portable way. Second, at any given point in time, the technology used in I/O adaptor hardware tends to lag behind that of the main computer system, due to economics. Consequently, applications that rely on out-board processing may not be able to exploit performance gains resulting from an upgrade of the host computer system. An exception are computations whose performance is bound by the characteristics of the device, e.g., network link speed. Performing such computations in the adaptor seems appropriate, since they cannot take advantage of increased host processing speed [BPP92].

With hardware streaming, no specific techniques are required for data transfer in the I/O subsystem. However, many of the issues discussed in this chapter may apply to the *internal* design of the adaptor boards.

#### 2.4.2 DMA-DMA Streaming

A second approach is for data to be transferred using DMA from a source device to buffers in main memory, where some buffer editing may occur under control of the operating system, and then, the data is transferred to a sink device using DMA (Figure 2.2, (b)). The CPU controls data transfers, may change the size of the data units and control information (headers), but remains removed from the data path. Unlike the previous approach, DMA-DMA streaming requires no special hardware other than DMA support on both the source and sink device adaptors. Consequently, generic devices (e.g., disks) can be used.

Two DMA I/O bus trips are required by this approach. It follows that the throughput is bounded by one half of the I/O bus bandwidth. In practice, the sustainable throughput is lower, since main memory accesses caused by concurrent CPU activity compete with the DMA transfers for main memory access, even if the I/O bus and memory bus are separated.

Two key techniques are required to keep the CPU removed from the data path in this approach: scatter-gather DMA support in the device adaptors, and an OS buffer manager that supports copy-free buffer editing. Support for gather DMA in the sink device adaptor is critical. Recall that a lazily evaluating buffer manager may cause a buffer to consist of multiple discontiguous fragments. In the absence of a gather capability, it is necessary to copy data units into contiguous space prior to a transfer to the sink device.

#### 2.4.3 OS Kernel Streaming

Now consider systems where software data manipulations are performed, but all the manipulations are executed within the privileged kernel protection domain; no user-level programs are involved. Clearly, the data must pass through the CPU/data cache (Figure 2.2, (c)), implying that the achievable throughput is bounded by the system's copy bandwidth. The goal is to keep the resulting CPU-memory data traffic to the minimum, namely two transfers. The solution is to integrate data manipulations—if there is more than one—using, for example, ILP. Note that data manipulations may include data movement from and to devices via PIO.

If a device supports both DMA and PIO, it may be beneficial to use PIO in this type of system, since programmed data movement can be integrated with other data manipulations. That is, instead of first using DMA and then loading/storing data to/from main memory, the CPU could directly load data from the source I/O adaptor, and store data to the sink I/O adaptor, bypassing main memory. This approach saves two DMA bus trips, which would otherwise compete with the CPU for memory access. However, it also trades memory accesses for potentially much slower load and store operations across the I/O bus. Which approach results in a more efficient data path depends on the relative performance of memory accesses and DMA transfers, versus PIO on the target hardware.

Unlike the previous methods, OS kernel streaming offers full programmability of the data path. However, all data manipulations must be performed in the kernel of the operating system. Applications and user-level servers are restricted to the set of data manipulations implemented by the kernel.

#### 2.4.4 User-Level Streaming

Finally, consider systems where data passes through the kernel, plus one or more user-level protection domains. These user-level domains could be part of a microkernel-based operating system, implement third-party servers for windowing, or be part of an application. In addition to the issues discussed in the previous subsections, the I/O subsystem designer is faced with protection domain boundaries. Protection boundaries are an obstacle to the integration of data manipulations. We conclude, therefore, that designers should make every effort to locate all data manipulation functions in the same domain. Protection also requires an efficient method for transferring data between domains.

Section 2.3.2 discussed several VM techniques for cross-domain data transfer. The use of such a facility is critical for data transfer between two user-level protection domains. Otherwise, two software copies are required for a user-to-user transfers on most systems from the source user domain to a kernel buffer and from the kernel buffer to the target user domain. Chapter 5 introduces a novel facility for cross-domain data transfer that performs better than existing techniques, and achieves an efficient end-to-end data path, both in monolithic and server-based operating systems.

As a special case, it is possible to transfer data between a user domain and the operating system kernel without extra cost if the transfer is combined with the data movement between I/O adaptor and main memory. That is, data is transferred directly between the I/O adaptor and the user buffer [Jac90, DWB<sup>+</sup>93]. However, with this approach, a potentially huge amount of buffer memory is required in a high-speed network adaptor. On the receiving end, the data be buffered in the adaptor until the receiving application asks for the data. On the transmitting side, transmitted data must be buffered in the network adaptor for potential retransmission, since no intermediate copy of the data exists in main memory. Due to the large bandwidth-delay product of high-speed networks, large amounts of data must be buffered for retransmission. Finally, this approach does not generalize to I/O data streams that are accessed in more than one user-level protection domain.

#### 2.4.5 Need for Integration

The API, cross-domain data transfer facility, and buffer manager must be integrated in a manner that takes into account their subtle interactions. Consider, for example, a system where the buffer manager is restricted to the kernel domain, a virtual copy facility is used for cross-domain data transfer, and the OS supports a UNIX-style API.

In this case, data units from the source device are placed in main memory buffers, and some buffer editing occurs as part of the in-kernel I/O processing; e.g., reassembly of network packets. When a data unit represented by a lazily evaluated buffer reaches the user/kernel boundary, it must be evaluated (copied into contiguous storage), despite the use of a virtual copy facility. The reason is that the interface defines data buffers to be contiguous. Since the API allows applications to specify an arbitrarily aligned buffer address and length, the buffer's first and last address may not be aligned with page boundaries. Consequently, the data transfer facility may be forced to copy the portion of the first and last page that is overlapped by the buffer.

Once in the application domain, more buffer editing may need to be performed. Since

the buffer management tool is not available at user-level, the application must either perform data copying, or perform its own lazily evaluating buffer management. In the latter case, another copy is required when data crosses the next domain boundary. After data is transferred back to the kernel, the semantics of the API allow the user program to reuse the data buffer instantly, which is likely to force the virtual copy facility to copy parts of the buffer. We conclude that despite the use of copy-avoiding techniques, multiple copies occur along the data path and these copies are an artifact of the poor integration of these techniques.

One problem is that the implementation of the buffer manager is local to the kernel domain; a global implementation is necessary to maintain the lazily evaluated representation of data buffers along the entire data path. A global abstract buffer type has the additional benefit that all domains (including applications) can perform copy-free buffer editing. A second problem is the API, which commonly does not permit a non-contiguous representation of buffers, and as a consequence, stands in the way of efficient data transfer. A potential third problem is the cross-domain data transfer facility's inability to efficiently support the transfer of non-contiguous buffer fragments.

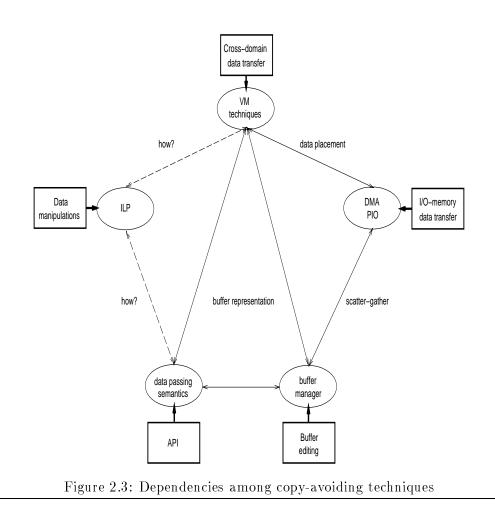

Figure 2.3 depicts some of the dependencies among the copy-avoiding techniques. The boxes represent situations where copies may occur along the data path, and the bubbles correspond to the appropriate copy-avoiding techniques. Edges indicate dependencies among the techniques that must be satisfied to achieve an efficient data path. For example, VM techniques for data transfer, the API's data passing semantics, and the buffer manager must agree on a common buffer representation. The dashed lines indicate that it is unclear how to effectively integrate ILP with API and data transfer facility, to permit integration of data manipulations across protection domain boundaries.

In conclusion, in the interest of minimizing main memory traffic, it is necessary to maintain a lazily evaluated representation of data buffers along the entire data path. This implies that all programs must deal with this representation of buffers. Consequently, a global buffer manager is needed that is integrated with the API and cross-domain transfer facility. The choice of a cross-domain data transfer method may further influence the design of a network adaptor. For example, shared virtual memory requires demultiplexing prior to the data transfer from adaptor to main memory.

# 2.5 A Buffer Abstraction for an Integrated Data Path

This section proposes an API that permits the integration of the API, buffer manager, and cross-domain data transfer facility to achieve an efficient end-to-end data path. The approach hinges on an abstract data type for data buffers called *IOData*. This section gives an overview of the IOData type design, discusses its use, and briefly sketches how it can be implemented using different buffer management schemes and cross-domain data transfer facilities.

In Section 2.3.5 we argued that the UNIX API has three problems with regard to the efficient transfer of I/O data. Its read and write system calls allow applications to specify data buffers with arbitrary alignment and length, they require contiguous data buffers, and they have copy semantics. These problems can be solved by adding a set of new

I/O operations to the API. These I/O operations take as arguments an *abstract data type* (ADT) that represents data buffers (instead of pointers), and these arguments are passed with *handoff* rather than copy semantics. The standard read and write systems calls can be maintained for backward compatibility, and the new operations can be used by new applications that require high-performance I/O.

## 2.5.1 The IOData Abstract Data Type

An instance of the IOData abstract data type represents a data buffer of arbitrary length. It encapsulates one or more physical buffers that contain the data. At any given time, the physical buffers may not be contiguous, mapped in the current domain, or even in main memory. The IOData type is *immutable*, i.e., once an instance is created with an initial data content, the content cannot be subsequently changed. IOData instances can be manipulated using a well-defined set of operations. An implementation of this abstract type—i.e., code that implements its operations—is included as part of a library in each protection domain. The exact form and syntax of IOData's operations depends on the programming language used, which may vary from domain to domain.

The use of the IOData type for data buffers has important advantages. First, it en-

sures that a single buffer representation can be maintained along the entire data path, permitting lazy buffer evaluation. Second, it isolates applications, user-level servers, and large parts of the kernel from details of buffer management and cross-domain data transfer. This increases portability of both applications and operating system, and permits the use of the most efficient buffer management and data transfer techniques on different platforms. Third, the IOData type gives applications access to efficient buffer manipulation operations, and eliminates the need for separate application-level buffer management.

The IOData type supports the following operations. An *allocate* operation creates a new instance of the requested size and allocates an appropriate number of physical buffers. During an initialization phase, the client is provided with a list of pointers to these physical buffers, for the purpose of initialization. A *share* operation creates a logical copy of an IOData instance; it does not actually copy the physical buffers. *Clip*, *split*, and *concatenate* operations implement the necessary buffer editing operations. A *retrieve* operation generates a list of pointers to the physical data buffer fragments, thereby allowing the client to access the data. A *mutate* operation is a combination of retrieve and allocate. It allows a client to read the data from an IOData instance, and store the perhaps modified data into a new IOData instance. The operation generates a list of pointer pairs, one referring to a fragment of the source, the other pointing to a physical buffer of the target. Finally, a *deallocate* operation destroys an IOData instance, and deallocates the physical buffers if no logical copies of the data remain.

## 2.5.2 Implementation

Consider an implementation of the IOData type. One key feature is that the implementation has complete control over the size, location, and alignment of physical buffers. Consequently, a variety of buffer management schemes are feasible. All buffers may be part of a system-wide pool, allocated autonomously by each domain, located in a shared VM region, or they may reside outside of main memory in an I/O adaptor. Physical buffers can be of a fixed size to simplify and speed allocation. The other key feature of the IOData type is its immutability. It allows the transparent use of page remapping, shared virtual memory, and other VM techniques for the cross-domain transfer of IOData instances. Virtual copying can be used with increased efficiency since physical buffers are guaranteed not to be written after a transfer. The implementation of the IOData abstract data type can also be based on fbufs, the I/O buffer management and cross-domain data transfer facility described in Chapter 5.

It is possible to extend an existing API (such as that of UNIX) to include input/output operations based on the IOData type. New applications that depend on high bandwidth (such as multimedia) can use the new interface. The conventional interface can be maintained for backward compatibility, at the cost of copying the data into contiguous storage. Applications that use the new interface, and consume/modify input data—rather than merely perform buffer editing—must be able to deal with the non-contiguous storage of IOData instances. For the large class of applications that access input data sequentially, the additional program complexity and runtime cost are negligible. Typically, the arrayindexing loop used to read data from a contiguous buffer must be nested in an additional loop that iterates over a list of buffers. Applications that require contiguous storage of data for efficiency must explicitly perform the copy (or use the old interface), thereby trading the copying cost for fast random access.

# 2.6 Concluding Remarks

This chapter shows that the bandwidth of the CPU-memory data path in modern, generalpurpose computer systems is within the same order of magnitude as the bandwidth of emerging high-speed I/O devices, and that this state of affairs is likely to persist for the foreseeable future. This makes it essential to minimize main memory traffic during the processing of I/O operations, in order to avoid a bottleneck in delivering high-speed network traffic to application programs. Moreover, cache memories do not significantly reduce main memory traffic during I/O operations, due to the poor locality of the corresponding memory accesses in current operating systems.

We identify the main causes of main memory traffic during network I/O operations, namely data transfer between I/O device and main memory, data transfer across protection domain boundaries, data manipulations, buffer management, and interfaces. Techniques are presented that can help eliminate or reduce memory traffic in each case. From this discussion, we draw a number of conclusions.